- 全部

- 默认排序

Cadence Allegro如何快速对齐器件 PCB设计过程中有一个环节是器件布局,器件的布局不但考虑电路的连通性,同时也考虑美观性,艺术性,所以器件布局尽可能整齐美观。 Allegro设计PCB过程中元件的对齐这要是通过栅格对齐的方式进行器件对齐,另一是用Align components对齐命令实现对齐的。 今天教大家如何使用“Align components”对齐命令快速对齐器件,操作方法如下:

一、课程详情这个是一个Cadence Allegro非常经典的 6 层一阶盲打孔设计,基于三星系列 S3C6410 ,全程讲解了通过Cadence Allegro,运用-阶盲埋孔的技术进行工控核心板卡的 PCB 设计教程视频,从前期的原理图导入,到后期输出生产文件( GERBER)的全过程。

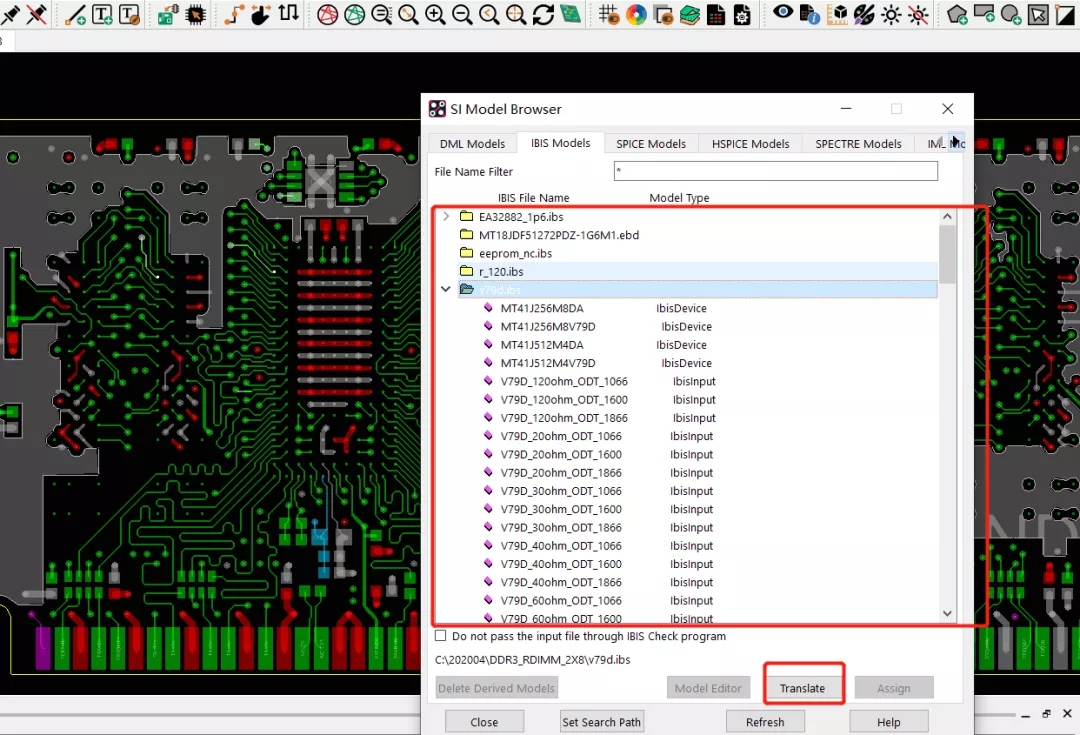

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

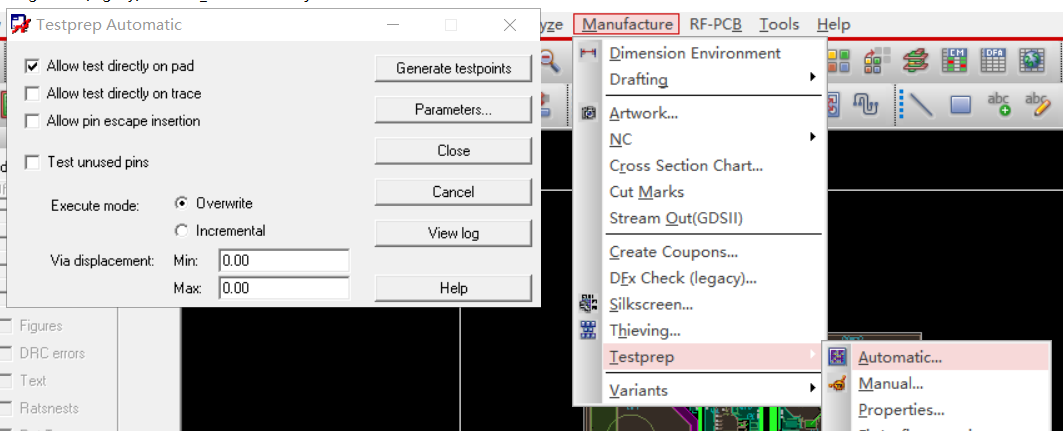

Cadence Allegro Allow test directly on pad:允许测试点在焊盘上,允许时将自动替换已有的过孔。Allow test directly on trace:允许测试点在信号线上,允许时测试点可以直接在信号线上。Allow pin escape insertion:允许从引脚上自动引出测试点。Test unused pins:无网络引脚添加测试点。

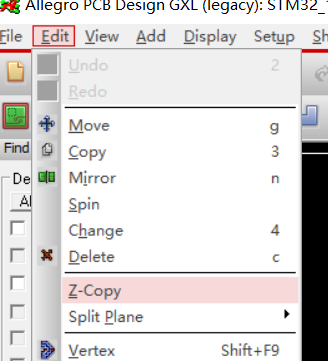

大面积敷铜就是将PCB上闲置的空间用铜箔填充,能起到美观和屏蔽噪声的效果,大面积敷铜可以直接使用Cadence Allegro敷铜命令,也可以用Z-Copy命令将地平面的铜箔直接复制到外层。Z-Copy的命令,执行菜单命令edit→Z-Copy,如图:

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

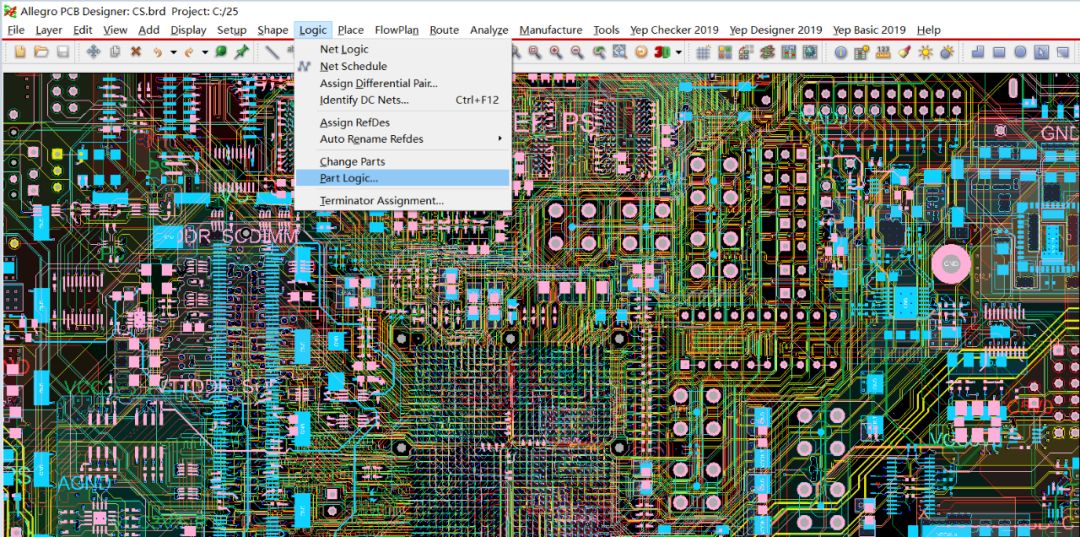

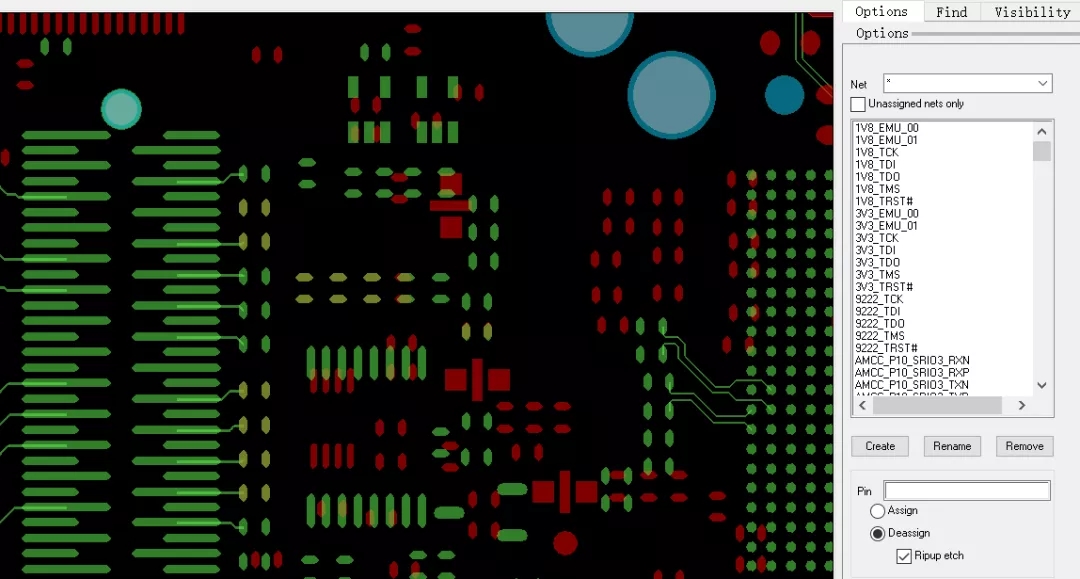

在项目实际的设计中我和小伙伴一样都遇到过很多麻烦的问题,有些时候原理图和PCB设计可能是由不同的工程师负责,由于种种原因可能需要在没有原理图的情况下直接对PCB进行操作。如更新元件封装和增加与删除元件等操作。接下来我们一起学习

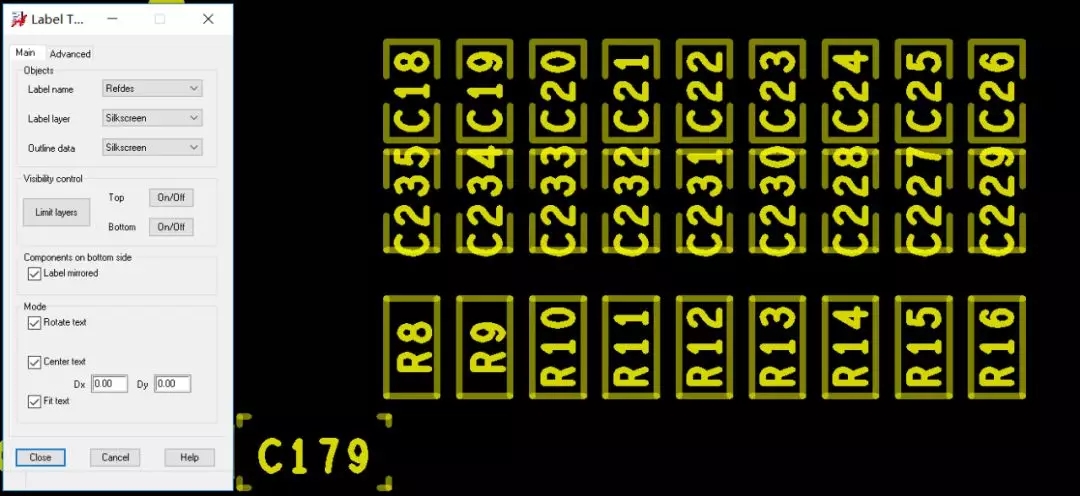

Allegro Productivity Toolbox组件所带来了很多高级命令,今天我们一起学的Label Tune就是其中一个。Label Tune是用来做批量的元件字符对齐操作的命令,可以支持对丝印、显示、装配层的字符对齐操作。我们知道PCB设计里面,丝印可以给贴片和识图的工程师提供一个位置参考,可以让工程师能够快速的找到元件在PCB上的位置。如下图所示,这样整齐的丝印排列可以让工程师快速定位元件位置。

扫码关注

扫码关注